## Intel<sup>®</sup> StrongARM\* SA-1110 Microprocessor Development Board

**User's Guide**

June 2000 Hardware Build Phase 5

Order Number: 278278-006

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The SA-1110 Development Board may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2000

\*Third-party brands and names are the property of their respective owners.

| 1 | Introdu    | uction                                                                                                                                                                                                                                                                           | 1–1                                                  |

|---|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|   | 1.1<br>1.2 | Related Documentation<br>SA-1110 Development Platform Overview                                                                                                                                                                                                                   |                                                      |

| 2 | Gettin     | ng Started                                                                                                                                                                                                                                                                       | 2–1                                                  |

|   | 2.1        | Physical Description         2.1.1       Unpacking the Intel® StrongARM* SA-1110 Development Board         2.1.2       Development JTAG         2.1.3       Intel® StrongARM* SA-1110 Development Board Software         2.1.4       Assembling the SA-1110 Development Platform | 2–1<br>2–5<br>2–5<br>2–5                             |

|   | 2.2<br>2.3 | Providing Power for Only the SA-1110 Development Board<br>Providing Power for the SA-1110 Development Board and the SA-1111<br>Development Module                                                                                                                                |                                                      |

|   | 2.4        | Using the ARM* ADS with the SA-1110 Development Platform<br>2.4.1 Angel* Firmware<br>2.4.2 Connecting the SA-1110 Development Platform to the Host<br>2.4.3 Bringing Up the Angel* Debug Monitor<br>2.4.4 Running an Application                                                 | 2–9<br>.2–10<br>.2–10<br>.2–10                       |

| 3 | Theory     | y of Operation                                                                                                                                                                                                                                                                   | 3–1                                                  |

|   | 3.1        | System Partitioning                                                                                                                                                                                                                                                              | 3–1                                                  |

| 4 | Hardw      | vare Considerations                                                                                                                                                                                                                                                              | 4–1                                                  |

|   | 4.1<br>4.2 | Xbus Expansion Headers                                                                                                                                                                                                                                                           | 4–1<br>4–2<br>4–2<br>4–3<br>4–3<br>4–3<br>4–3<br>4–3 |

|   | 4.3        | Intel® StrongARM* SA-1110 GPIO Usage                                                                                                                                                                                                                                             | 4–6                                                  |

|   | 4.4        | <ul> <li>Register Descriptions</li> <li>4.4.1 Intel® StrongARM* SA-1110 System Configuration<br/>Register SCR</li> <li>4.4.2 SA-1110 Development Board Control Register<br/>BCR 0x1200,0000</li> <li>4.4.3 SA-1110 Development Board Status Register 0x1200,0000</li> </ul>      | 4–8                                                  |

|   | 4.5<br>4.6 | System Reset         System Displays         4.6.1       LED Displays         4.6.2       LCD Displays         4.6.2.1       Sharp 3.9" Reflective Color         4.6.2.2       Memory Pixel Representations Versus Physical Pixel Interface                                      | .4–15<br>.4–16<br>.4–16<br>.4–16<br>.4–16            |

|       |            | 6.2.3    |                                                      |        |

|-------|------------|----------|------------------------------------------------------|--------|

|       |            | 6.2.4    |                                                      |        |

| 4.7   |            | -        |                                                      |        |

|       | 4.7.1      | Keypac   | 1                                                    | . 4–18 |

|       | 4.7.2      | Debug    | Switches                                             | .4–18  |

|       | 4.7.3      | Functio  | n Switches                                           | .4–18  |

|       | 4.7.4      |          | nalyzer Support                                      |        |

| 4.8   | SMBus      | •        |                                                      |        |

| 4.9   |            |          |                                                      |        |

| 4.9   |            |          |                                                      |        |

| 4.10  | •          |          |                                                      |        |

|       | 4.10.1     |          | System Design Benefits                               |        |

|       | 4.10.2     |          | System Design                                        |        |

|       |            | 10.2.1   | 1.5V Core Power                                      |        |

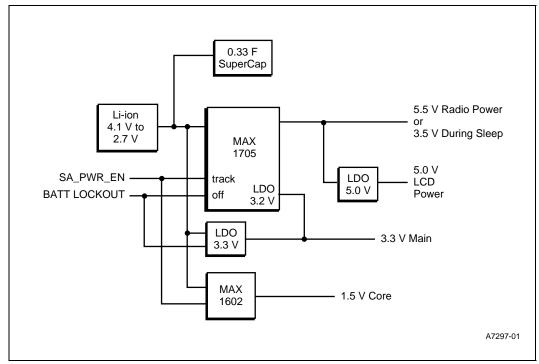

| 4.11  | Power for  |          | I® StrongARM* SA-1110 Development Board              |        |

|       | 4.11.1     | 3.3 V N  | Iain System Power Design Considerations              | . 4–22 |

|       | 4.11.2     | MAX17    | 05 Boost Converter and MIC5219 LDO Linear Regulator. | . 4–23 |

|       | 4.         | 11.2.1   | Sleep Mode                                           | .4–24  |

|       | 4.         | 11.2.2   | Virtual Backup Battery                               |        |

|       |            | 11.2.3   | Linear Boost Bootstrap System                        |        |

|       | 4.         | 11.2.4   | Radio Power                                          |        |

|       |            | 11.2.5   | LCD Power                                            |        |

|       | 4.         | 11.2.6   | System Power Limits                                  |        |

| 4.12  | Audio Svs  | tems     | ,                                                    |        |

|       | 4.12.1     |          | Codec                                                |        |

|       | 4.12.2     |          |                                                      |        |

|       | 4.12.2     |          | Codec Interface                                      | -      |

|       |            |          |                                                      |        |

|       | 4.12.4     |          | none and Speaker                                     |        |

|       | 4.12.5     |          | 0 Development Board Stereo Codec Sampling Rates      |        |

|       | 4.12.6     |          | Codec and Soft Modem                                 |        |

|       | 4.12.7     |          | System Routing and Mixing Diagram                    |        |

|       |            |          | UDA1341 Loopback Mode                                |        |

|       |            | 12.7.2   |                                                      |        |

| 4.13  | Radio Inte | erface   |                                                      | . 4–33 |

|       | 4.13.1     | CDMA     | Radio Module                                         | . 4–34 |

|       | 4.13.2     | GSM R    | adio Module                                          | .4–34  |

|       | 4.13.3     |          | oth Radio Module                                     |        |

| 4.14  | Quiet Aler |          |                                                      |        |

| 4.15  |            |          | nmunications                                         |        |

| 4.16  |            |          |                                                      |        |

| 4.10  |            |          | ign                                                  |        |

| 4.17  |            | •        | •                                                    |        |

|       | 4.17.1     |          | 0 Core Clock Frequency                               |        |

|       | 4.17.2     |          | ed Video                                             |        |

|       | 4.17.3     |          | Dutput Interlaced Timing Generation                  |        |

|       | 4.17.4     | Interlac | ed Display Buffer                                    | .4–36  |

| Analo | a. I/O     |          |                                                      | 51     |

|       | •          |          |                                                      |        |

| 5.1   | UCB1300    | Analog   | IO                                                   | 5–1    |

|       | 5.1.1      | Battery  | Voltage                                              | 5–1    |

|       | 5.1.2      | -        | Temperature                                          |        |

|       | 5.1.3      | -        | Spare                                                |        |

| 5.2   |            | -        |                                                      |        |

|       |            |          |                                                      | -      |

6

А

| 5.3     | Touch Sc    | reen                                                    | 5–3 |

|---------|-------------|---------------------------------------------------------|-----|

| Syster  | n Power M   | anagement                                               | 6–1 |

| 6.1     | Battery P   | ower                                                    | 6–1 |

| 6.2     |             | anagement                                               |     |

|         | 6.2.1       | Low-Cost Battery Management                             |     |

|         | 6.2.2       | Smart Battery Management                                |     |

|         | 6.2.3       | Battery Physical Interface                              |     |

|         | 6.2.4       | Battery Capacity                                        | 6–3 |

|         | 6.2.5       | Battery Safety                                          | 6–3 |

|         | 6.2.6       | Fuel Gauging                                            |     |

|         | 6.2.7       | Special Handling and Storage Requirements for Batteries | 6–5 |

| In-Circ | uit Program | nming                                                   | 7   |

| A.1     | In-Circuit  | Programming of Flash Devices                            | 7   |

| A.2     |             | Programming of CPLD Devices                             |     |

|         |             |                                                         |     |

## **Figures**

| 1-1 | Preliminary Intel® StrongARM* SA-1110 Developer Platform         | 1–2  |

|-----|------------------------------------------------------------------|------|

| 1-2 | Preliminary Cross-Sectional view of SA-1110 Development Platform | 1–3  |

| 2-1 | Intel® StrongARM* SA-1110 Development Board, Side 1              | 2–3  |

| 2-2 | Intel® StrongARM* SA-1110 Development Board, Side 2              | 2–4  |

| 2-3 | Li-Ion Battery Location                                          | 2–6  |

| 2-4 | Master Power Clip Location                                       | 2–7  |

| 2-5 | AC Power Input Jack Location                                     | 2–7  |

| 2-6 | Li-Ion Battery Location                                          | 2–8  |

| 2-7 | AC Power Input Jack Location                                     | 2–9  |

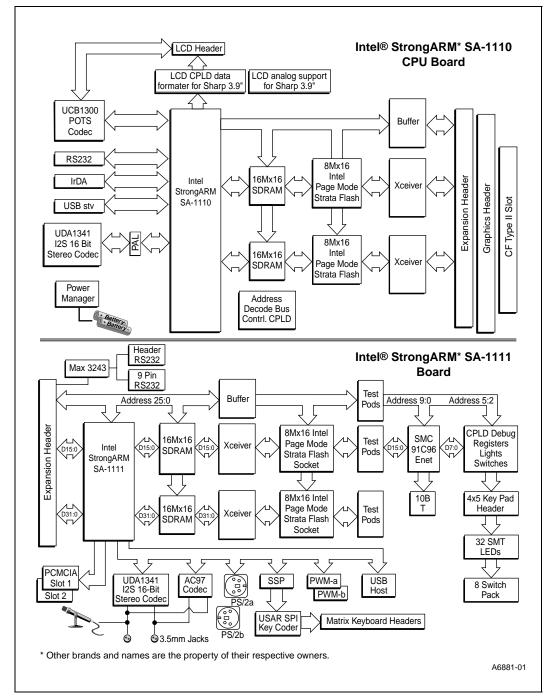

| 3-1 | Intel® StrongARM* SA-1110 Development Platform Block Diagram     | 3–2  |

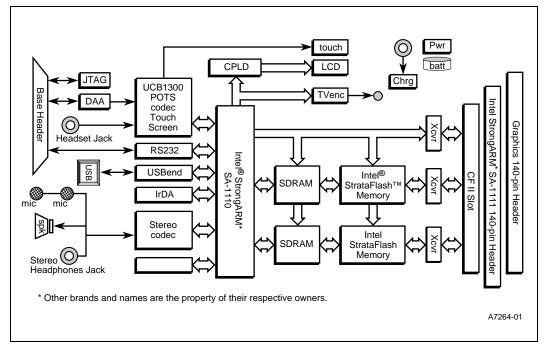

| 3-2 | Intel® StrongARM* SA-1110 Development Board Inputs and Outputs.  | 3–3  |

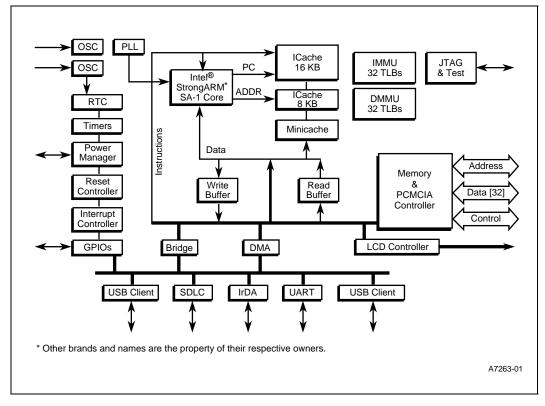

| 3-3 | Data Flow in the SA-1110 Microprocessor                          | 3–4  |

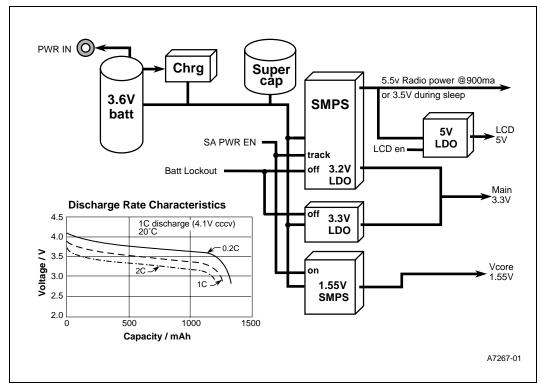

| 4-1 | Li-ion Discharge Curves                                          | 4–21 |

| 4-2 | Linear Boost Bootstrap Power System                              |      |

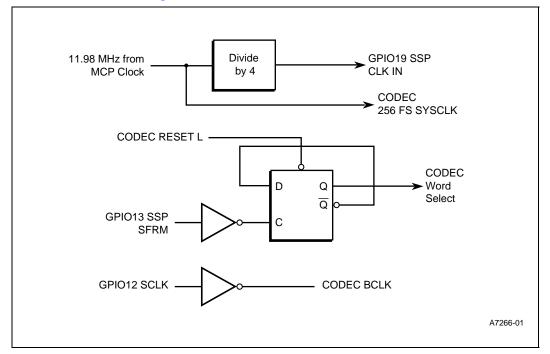

| 4-3 | Stereo Codec Glue Logic                                          |      |

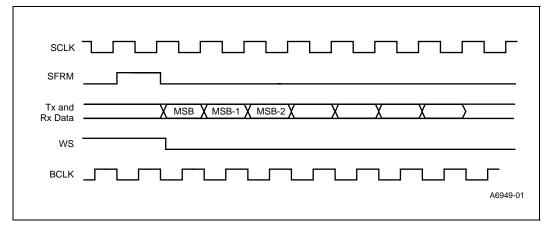

| 4-4 | UDA1341 Interface Timing                                         |      |

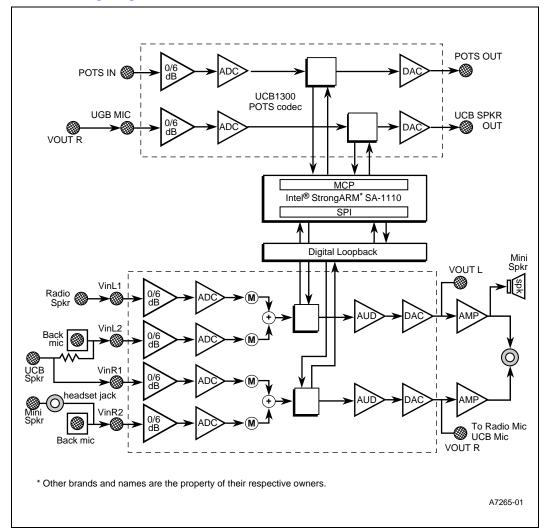

| 4-5 | Audio Mixing Diagram                                             |      |

| 4-6 | Waking Circuit                                                   |      |

| 4-7 | Interlaced Frame Buffer                                          |      |

## **Tables**

| 4-1 | System Memory Map                          | .4–2 |

|-----|--------------------------------------------|------|

|     | GPIO Usage for Intel® StrongARM* Platforms |      |

| 4-3 | UCB 1300 CODEC                             | .4–6 |

| 4-4 | GPIO Pin Descriptions                      | .4–7 |

|     | System Configuration Bit Descriptions      |      |

| Board Control Register            | 4–11                                                                                                         |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------|

| Board Status Register             |                                                                                                              |

| LED Descriptions                  | 4–16                                                                                                         |

| ADC Input Pin Descriptions        | 5–1                                                                                                          |

| Battery Voltage Level Indications | 5–2                                                                                                          |

| Battery Temperature Indications   | 5–2                                                                                                          |

|                                   | Board Status Register<br>LED Descriptions<br>ADC Input Pin Descriptions<br>Battery Voltage Level Indications |

Introduction

# intel®

# Introduction

The Intel<sup>®</sup> StrongARM\* SA-1110 Microprocessor (SA-1110) is a highly integrated communications microcontroller that incorporates a 32-bit StrongARM\* RISC processor core, system support logic, multiple communication channels, an LCD controller, a memory and PCMCIA controller, and general-purpose I/O ports. For more information about the SA-1110 device, see the *Intel<sup>®</sup> StrongARM*<sup>\*</sup> SA-1110 Microprocessor Developer's Manual, order number 278240.

The Intel<sup>®</sup> StrongARM\* SA-1111 Microprocessor Companion Chip (SA-1111) is a companion chip to the SA-1110, providing a variety of functions suitable for use in a high-performance handheld computer system. The SA-1111 brings a new level of integration to small systems, providing a variety of I/O functions that enable complete systems to be built with very little "glue" logic. In addition to a complete USB Host Controller, the SA-1111 includes extensive support for PCMCIA and Compact Flash (CF), two PS/2 ports, two industry-standard serial ports, and other I/O capabilities. It can acquire the system memory bus and do DMA transfers to system memory (EDO or SDRAM) with its high-performance memory controller. For more information about the SA-1111 device, see the Intel<sup>®</sup>StrongARM\* SA-1111 Companion Chip Developer's Manual, order number 278242.

The Intel<sup>®</sup> StrongARM\* SA-1110 Development Platform (SA-1110 Development Platform) order number SA111XDEVKIT is based upon these devices and is composed of a two board set<sup>1</sup>:

- Intel<sup>®</sup> StrongARM\* SA-1110 Development Board (SA-1110 Development Board) order number SA1110DEVBD.

- Intel<sup>®</sup> StrongARM\* SA-1111 Companion Chip Development Module (SA-1111 Development Module) order number SA1111DEVMOD.

- *Note:* This document and module are for the Phase 5 hardware build of this product. For the latest information and updates, see the hardware release notes that are provided in hardcopy format, the software readme.txt files that are provided in the software kits, and related specification updates on Intel's website for developers.

Figure 1-1 shows the preliminary front view of the SA-1110 Development Platform and Figure 1-2 shows a preliminary cross-sectional view.

<sup>1.</sup> Though not included with the kit, the SA-1110 Development Platform also supports a graphics module.

#### Figure 1-1. Preliminary Intel<sup>®</sup> StrongARM\* SA-1110 Developer Platform

Introduction

Figure 1-2 shows a preliminary sideview of the SA-1110 development board:

Figure 1-2. Preliminary Cross-Sectional view of SA-1110 Development Platform

The modular design of the SA-1110 Development Platform makes it a flexible, extendable and reusable design that supports<sup>1</sup> the following requirements:

- Targeted for hand-held applications

- Multiple OS development platform

- Third-party vendor graphics accelerator development platform

- Development platform for SA-1111 Companion Chip

- SA-1110 Development Board may be used as a palm PC reference design and development platform

- SA-1110 Development Board may be used as host board for PCI bridge ASIC/FPGA and a Windows CE reference platform

- Battery powered design example

- Power management and battery management including SMBus and SBS development platform

- RF communications development board with interfaces for CDMA and GSM and Bluetooth<sup>2</sup> RF modules

<sup>1.</sup> The SA-1110 Development Platform has not been certified as being compliant with FCC, CE, UC, or PTT telephone standards or regulations.

<sup>2.</sup> For the Phase 5 release of this product, formal Bluetooth interface specifications were not available. For more information, see section Section 4.13.3.

## 1.1 Related Documentation

Other documentation that may be helpful while reading this document are described in the following table:

| Title                                                                                                                  | Location                                                                |  |

|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

| Intel <sup>®</sup> StrongARM* SA-1110 Microprocessor Advanced<br>Developer's Manual, order number: 278240              |                                                                         |  |

| Intel <sup>®</sup> StrongARM* SA-1110 Microprocessor Specification Update, order number: 278259                        |                                                                         |  |

| Intel <sup>®</sup> StrongARM* SA-1110 Development Board Parts List, order number: 278280                               |                                                                         |  |

| Intel <sup>®</sup> StrongARM* SA-1110 Development Board Schematics, order number: 278279                               |                                                                         |  |

| Intel <sup>®</sup> StrongARM* SA-1111 Microprocessor Companion Chip<br>Developer's Manual, order number: 278242        | Intel's website for developers is at: <u>http://developer.intel.com</u> |  |

| Intel <sup>®</sup> StrongARM* SA-1111 Microprocessor Companion Chip Specification Update, order number: 278260         |                                                                         |  |

| Intel <sup>®</sup> StrongARM* SA-1111 Companion Chip Development<br>Board Schematics, order number: 289282             |                                                                         |  |

| Intel <sup>®</sup> StrongARM* SA-1111 Companion Chip Development<br>Board Parts List, order number: 278283             |                                                                         |  |

| Intel <sup>®</sup> StrongARM* SA-1111 Companion Chip Development<br>Board User's Guide, order number: 278281           |                                                                         |  |

| Intel <sup>®</sup> StrongARM* SA-1110 Development Board - Windows*<br>CE Software Kit User Guide, order number: 278322 |                                                                         |  |

| The ARM Debug Monitor: Angel                                                                                           | ARM's website is at:                                                    |  |

| ARM Architecture Reference Manual                                                                                      | http://www.arm.com                                                      |  |

## 1.2 SA-1110 Development Platform Overview

The SA-1110 Development Board, the SA-1111 Development Module, and the graphics accelerator boards are a flexible software and hardware development environment and example design. When the SA-1110 Development Board is used as a development system, the SA-1111 Development Module is also required to provide Ethernet, serial port, LEDs and logic analyzer support.

The SA-1110 Development Board has the following resources and features:

- Up to 32MB fast page mode Intel<sup>®</sup> StrataFlash<sup>™</sup> memory

- Up to 64MB 100 MHz SDRAM

- Un-buffered main memory interface allows highest possible SDRAM memory bandwidth

- Small form factor 3.5" x 5" x 0.5" (same size as the Sony Nino\*)

- Phillips Semiconductor UCB1300\* codec supports microphone, speaker, POTS line soft modem DAA connections and touch screen

- Phillips Semiconductor UDA1341\* stereo codec supports high quality 16 bit stereo audio record and playback

- Infra-red interface for IrDA data links up to 4Mb

- Battery powered, using high efficiency DC-DC converters and a single Lithium ion (Li-ion) cell

- Smart battery technology development platform and reference design when used with smart battery packs

- Integrated 3.9" reflective color TFT LCD and touch screen

- Optional 8" color passive LCD for use with GFX companion chip

- Two expansion headers for the SA-1111 Development Module, the graphics accelerator board, or other boards

- · Built in mini speaker and two microphones

- Built in quiet alert vibration motor

- One type II Compact Flash socket (available only when the SA-1111 Development Module and graphics accelerator boards are not present)

- USB slave port for PC synchronization and battery trickle charge

- RF module interface connector for CDMA, GSM and Bluetooth modules up to 4 Watts

- Base station connector for JTAG programming, RS232, power input, and telephone

The SA-1111 Development Module has the following features<sup>1</sup>:

- Expansion Flash bank. Up to 32MB socketed fast page mode StrataFlash memory

- Expansion SDRAM bank (up to 64MB 50MHz SDRAM)

- Supports UDA1341 stereo codec for high quality 16 bit stereo audio record and playback

- Supports AC97 stereo codec for high quality 16 bit stereo audio record and playback

- Form factor is six inches by five inches by 1.38 inches

- Built in microphone

- One type II PCMCIA socket

- One type II Compact Flash socket

- USB host port

- USB host plug and power control device

- Two PS2 ports

- Logic analyzer pods

- 32 LEDs to display program debug data

- 10BASE-T Ethernet controller

- Debug serial ports (RS-232)

<sup>1.</sup> For more information about the SA-1111 Development Module, see *the Intel® StrongARM\* SA-1111 Companion Chip Development Module User's Guide.*

The graphics accelerator board has the following features<sup>1</sup>:

- Third-party high performance graphics accelerator

- Two head display support; Analog XGA and LCD XGA

- Direct connection for Sharp LM8V31 dual scan STN VGA color panel with backlight and touch screen

<sup>1.</sup> For more information about the graphics accelerator board, see the third-party documentation.

## -Getting Started

This SA-1110 Development Board is supplied as a mother board and functions as both a standalone handheld PC device as well as a development platform when used with the SA-1111 Development Module.

This chapter provides a physical description of the SA-1110 Development Board and describes how to:

- Unpack the card and give it a visual inspection

- Verify the SA-1110 Development Board kit contents

- Install the provided hardware

## 2.1 Physical Description

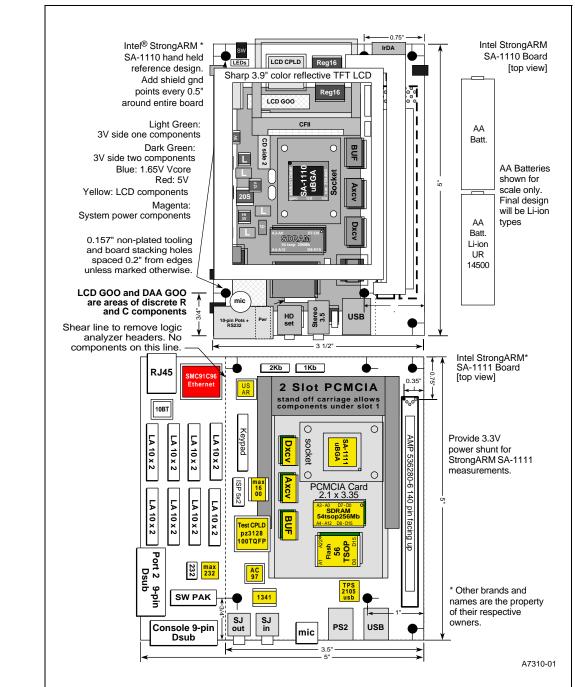

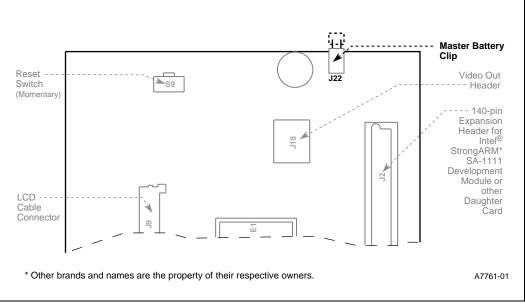

Figure 2-1 and Figure 2-2 shows the physical layout of the SA-1110 Development Board. The SA-1110 Development Board uses a 6-layer, micro-via, double-sided surface mount technology.

The following components and systems are on side one of the SA-1110 Development Board:

- LCD cable connector—50-pin connector for the Sharp 3.9" LCD display

- Touch screen header—Four-pin connector for the touch screen connector

- Intel StrataFlash<sup>™</sup> Memory—One of two 128 Mbit Intel StrataFlash memory components for storage of the operating system and applications

- Spare ADC input—An analog to digital converter that could be used as a photo-sensor input to sense ambient light for background light control

- Battery temperature sensor—Senses temperature of the Li-ion battery

- Base station—14-pin connector for Joint Test Action Group (JTAG) programming, RS232, power input jack, and telephone

- Headset jack 2.5 mm—2.5 mm standard telephony headset connector (earphone and microphone)

- Stereo jack 3.5 mm—standard stereo headphone 3.5 mm connector

- USB Type B connector—Universal Serial Bus, four-pin end point connection (slave) for host communications

- Microphone connector—accepts Electret type microphone

- Radio connector—30 pin connector that accepts CDMA, GSM, or Bluetooth<sup>1</sup> radio modules

- SDRAM—One of two 128 Mbit SDRAM storage devices

- Intel<sup>®</sup> StrongARM\* SA-1110 Microprocessor—Small size, low power, high performance, 32bit StrongARM processor.

<sup>1.</sup> For the phase 5 release of this product, formal Bluetooth interface specifications were not available. For more information, see Section 4.13.3.

- 140-pin expansion header—Main connector for SA-1111 Development Module (daughter) or third-party daughter cards

- Video out header-Five-pin connector that provides composite video

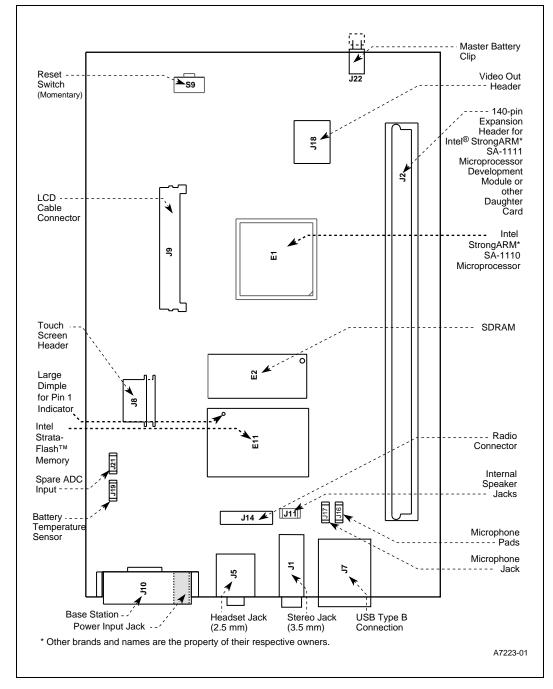

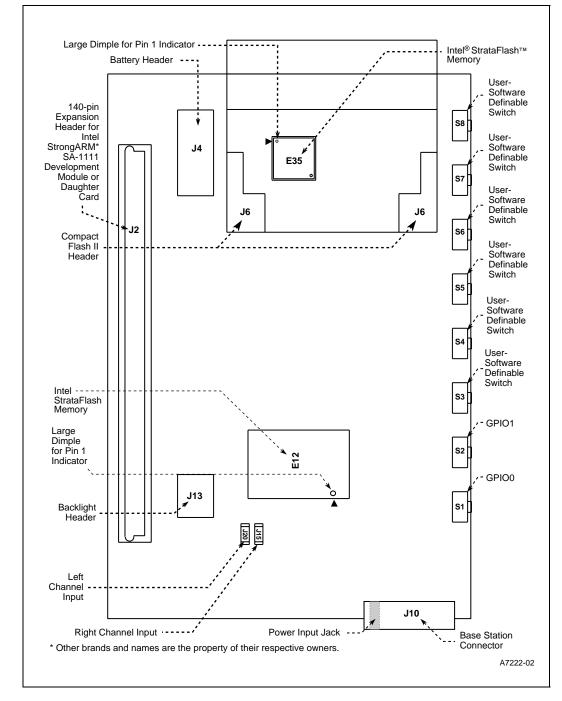

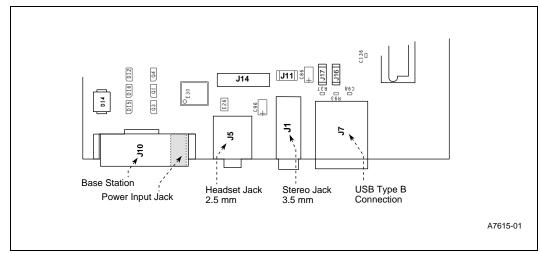

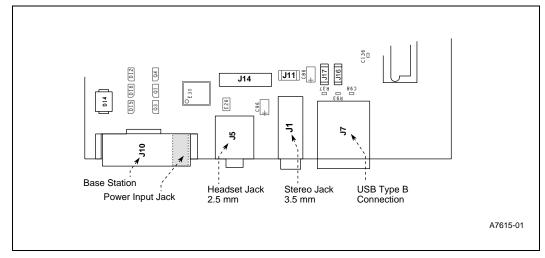

The following components and systems are on side two of the SA-1110 Development Board:

- Base station connector—14-pin connection for JTAG programming, RS232, power input jack, and telephone

- GPIO 0 switch—Manual override for GPIO 0

- GPIO 1 switch—Manual override for GPIO 1

- User software definable switches—Eight push-button switches for user software definable signals

- Battery headers-Ten-pin connector for battery temperature and status detection

- Compact Flash II header—50-pin connector used for Ethernet and memory expansion

- Backlight header—Five-pin connector for backlighting the LCD display

- Left channel input—Half of stereo input

- Right channel input—Half of stereo input

- Intel StrataFlash<sup>™</sup> Memory—One of two 128 Mbit Intel StrataFlash memory components for the operating system and applications

- SDRAM—One of two 128 Mbit SDRAM

- 140-pin expansion header—Main connector for SA-1111 Development Module (daughter) or third-party daughter cards

#### Figure 2-1. Intel<sup>®</sup> StrongARM\* SA-1110 Development Board, Side 1

### Figure 2-2. Intel<sup>®</sup> StrongARM\* SA-1110 Development Board, Side 2

### 2.1.1 Unpacking the Intel<sup>®</sup> StrongARM\* SA-1110 Development Board

- *Warning:* This board contains electronic components that are susceptible to permanent damage from electrostatic discharge (static electricity). To prevent electrostatic discharge, it is supplied in an antistatic bag. When handling the board, risk of damage can be alleviated by following a few simple precautions:

- Remove the board from the bag only when you are working on an antistatic, earthed surface and wearing an earthed antistatic wrist strap.

- Keep the antistatic bag that the card was supplied in; if you remove the board from a system, store it back in the bag.

- Do not touch the gold contacts.

### 2.1.2 Development JTAG

The SA-1110 Development Board uses the JTAG interface to program the PZ3128 and PZ3064 Complex Programmable Logic Devices (CPLDs). This code can be downloaded from Intel's website for developers.

The same JTAG loop also includes the SA-1110 component. With the appropriate software installed, the SA-1110 JTAG port hardware can be used to program the flash memories at a slow rate. However, the SA-1110 JTAG port does not support JTAG In-Circuit Emulation (ICE).

### 2.1.3 Intel<sup>®</sup> StrongARM\* SA-1110 Development Board Software

The following source and executable files are available from the StrongARM section in the developer's area on the Intel website:

- Angel debug monitor Software component for StrongARM based on ARM software that loads an application from a remote host computer or application flash.

- Set of microHal libraries Lowest level software that provides initialization for the StrongARM evaluation boards. This layer, provided as source-code for a library, resides between the actual hardware and any Real Time Operating System (RTOS) or user application.

- Diagnostics A set of test programs that analyze the functions of SA-1110 Development Boards and SA-1111 Development Modules.

- Sample I/O drivers Available for developers using Windows\* CE.

### 2.1.4 Assembling the SA-1110 Development Platform

The 140-pin connectors are very fragile on the SA-1110 Development Board and the SA-1111 Development Module. Care must be taken when assembling or disassembling these modules. For information about assembling procedures, see the *Intel<sup>®</sup> StrongARM\* SA-1111 Microprocessor Development Module User's Guide*.

*Caution:* If the 140-pin connector is damaged due to improper assembly, the reader must contact their Intel Sales representative for module replacement.

### 2.2 Providing Power for Only the SA-1110 Development Board

Use the following procedure to provide power only for the SA-1110 Development Board. To provide power for the SA-1110 Development Board and the SA-1111 Development Module, see Section 2.3.

- *Caution:* The following procedure assumes that the jumper (shunt) for J22, the Master Power Clip for the Li-ion battery, has been removed and that all power associated with the SA-1110 Development Board is off. For more information about Li-ion battery considerations, see Chapter 6.

- *Note:* A very high value capacitor of 0.33 Farads (super cap) is connected in parallel with the power input from J10. This capacitor provides enough power to support the system for several minutes in sleep mode when power from J10 is removed.

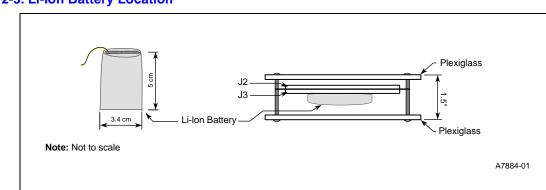

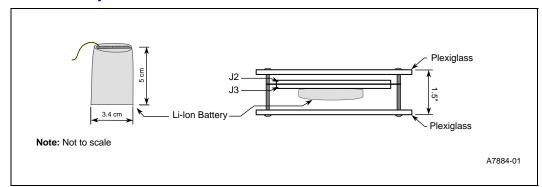

- 1. Verify that the Li-Ion battery is installed on the SA-1110 Development Board and that the battery harness is connected to J4 (see Figure 2-3 for the location of the Li-Ion battery).

#### Figure 2-3. Li-Ion Battery Location

2. Verify that the jumper (shunt) for J22 is **inserted** on the Master Power Clip (J22 should appear covered).

#### Figure 2-4. Master Power Clip Location

- 3. Select the appropriate AC adapter to DC converter device (wall brick) depending upon whether you are in a 110-volt or 220-volt environment.

- 4. Insert the power jack that is connected to the wall brick into J10 (see Figure 2-5 for the location of J10).

#### Figure 2-5. AC Power Input Jack Location

- *Note:* The power jack may have to be rotated to its flat side to accommodate any other connectors in J10.

- 5. Plug in the wall-brick into an AC outlet.

- 6. See the Intel® StrongARM\* SA-1110/SA-1111 Development Kit Quick Start User's Guide file for success and failure indications of start-up diagnostic results and how to proceed.

To disconnect power, remove the power jack from J10 and remove the Master Power Clip from J22 and wait for the super cap to discharge (typically less than 5 minutes).

*Note:* If sleep mode was entered as a result of VDD\_FAULT or BATT\_FAULT signals, GPIO 0 and GPIO 1 are the only wake up events that can bring the SA-1110 out of sleep mode.

### 2.3 Providing Power for the SA-1110 Development Board and the SA-1111 Development Module

Use the following procedure to provide power for the SA-1110 Development Board and the SA-1111 Development Module. To provide power for only the SA-1110 Development Board, see Section 2.2.

- *Caution:* The following procedure assumes that all power associated with the SA-1110 Development Board is off. For more information about Li-ion battery considerations, see Chapter 6.

- *Note:* A very high value capacitor of 0.33 Farads (super cap) is connected in parallel with the power input from J10. This capacitor provides enough power to support the system for several minutes in sleep mode when power from J10 is removed.

- 1. Disconnect the battery harness from J4 and remove the Li-Ion battery from the SA-1110 Development Board (see Figure 2-6 for the location of the Li-Ion battery).

#### Figure 2-6. Li-Ion Battery Location

- 2. Assemble the SA-1110 Development Board with the SA-1111 Development Module, as described in the *Intel*® *StrongARM*\* *SA-1111 Companion Chip Development Board User's Guide*.

- 3. Select the appropriate AC adapter to DC converter device (wall brick) depending upon whether you are in a 110-volt or 220-volt environment.

4. Insert the power jack that is connected to the wall brick into J10 (see Figure 2-7 for the location of J10).

#### Figure 2-7. AC Power Input Jack Location

- *Note:* The power jack may have to be rotated to its flat side to accommodate any other connectors in J10.

- 5. Plug in the wall-brick into an AC outlet.

- 6. See the *Intel*® *StrongARM*\* *SA-1110 Development Board Quickstart* file for success and failure indications of start-up diagnostic results and how to proceed.

To disconnect power, remove the power jack from J10 and wait for the super cap to discharge (typically less than 5 minutes).

*Note:* If sleep mode was entered as a result of VDD\_FAULT or BATT\_FAULT signals, GPIO 0 and GPIO 1 are the only wake up events that can bring the SA-1110 out of sleep mode.

### 2.4 Using the ARM\* ADS with the SA-1110 Development Platform

The ARM Developer Suite (ADS) is provided in the SA-1110 Development Platform kit. The ARM ADS is a cross-development tool set for ARM processors and is provided with an integrated development environment. The ARM ADS includes a debugger that allows the debugging of applications running on the target SA-1110 Development Platform.

When running the ARM debugger, one part runs on the host (this part includes the user interface) and the other part runs on the target (the SA-1110 Development Platform). The host and target interact across a communications channel. By default, the SA-1110 Development Platform uses its RS232 port to communicate with the host. The software that runs on the target is called the *remote debug stub* or *debug monitor*. The debug monitor used with the SA-1110 Development Platform is a program called Angel.

#### 2.4.1 Angel\* Firmware

To use the ARM ADS with the SA-1110 Development Platform, Angel must be resident. See the Angel readme file for information on installing Angel.

### 2.4.2 Connecting the SA-1110 Development Platform to the Host

After installing the ARM ADS on the host system, connect the SA-1110 Development Board to the host using the base station cable that is supplied in the SA-1110 Development Platform kit. This split cable contains the Dsub9 serial port, Dsub25 JTAG, and RJ11 phone jack connectors. Connect the Dsub9 connector to the RS-232 serial port on the host. The black Base Station connector of the split cable containing the POTS and RS-232 signals must be connected to the Base Station header on side 1 (J10) of the SA-1110 Development Board.

The same serial connections and cable as described in the preceding paragraph can be used and is the recommended method for providing serial communications between the host and SA-1110 Development Platform when the companion SA-1111 Development Module is attached. For this to work, ensure that switchpak 2 (SW2), switch 3 (SW2-3) on the SA-1111 Development Module is in the ON position. For the location of SW2, refer to the SA-1111 Development Module User's Guide. Alternatively, serial communications between the host and target can be provided by the double-female Dsub9 terminated RS232 cable that comes in the SA-1111 Development Module kit and the serial ports (UART1 and UART3) on the SA-1111 Development Module. Refer to the *Intel*® StrongARM\* *SA-1111 Development Module User's Guide* and the Angel software kit's readme.txt for more information on using those serial ports.

The 9-pin RS232 cable connected to the Base Station serial port (J10) on the SA-1110 Development Board cannot be connected at the same time as the UART1 serial port (J16) on the SA-1111 Development Module. Connecting them at the same time will corrupt the data on the UART1.

### 2.4.3 Bringing Up the Angel\* Debug Monitor

To configure the debug environment, power up the SA-1110 Development Platform and invoke the ARM AXD Debugger on the host system. Select the Options menu and choose the Configure Target option. In the Choose Target dialog, select the ADP target and press the "Configure" button. The Remote\_A Connection dialog appears. Press the Select button and choose the ARM serial driver. Press the "Configure" button. The Setup Serial Connection dialog will appear. Select the appropriate serial port (COM1..4) that is being used on the host for communicating to the SA-1110 Development Board. Select 115200 from the Baud Rate drop-down list. Only reduce the connection speed if you experience communications problems. Press "OK".

The following settings also should be made in the Remote\_A Connection dialog:

Heartbeat - Should be disabled (not checked)

Endian - "Little" should be selected

Channel Viewers - Should be disabled (not checked)

Press "OK" in the Remote\_A Connection dialog box to save the new settings. Press "OK" in the Choose Target box to accept the ADP target and activate remote debugging. A banner is printed in the RDI Log window of the AXD Debugger announcing the presence of the Angel Debug Monitor on the SA-1110 Development Platform.

### 2.4.4 Running an Application

The ARM ADS comes with some example applications that can be built and run. Follow the instructions above under Section 2.4.2 and connect the SA-1110 Development Platform to the host. On the host, invoke CodeWarrior for ARM Developer Suite. From the Files menu, select Open and navigate to the directory where the ARM SDK is installed. By default this directory is Program Files\ARM\ARM Developer Suite. Open the random number test project file, randtest.mcp, that can be found in Program Files\ARM\ARM Developer Suite\Examples\explasm. A window for the randtest project will appear. From the Project menu, select the "Make" option. The output window will display the progress and status of the build; there should be no errors.

Before running the randtest application, ensure that the SA-1110 Development Platform is connected to the host and apply power to it. It is assumed that the connections and remote configuration options have already been properly set as described in the previous Section 2.4.2 and Section 2.4.3. From the main CodeWarrior window select the Project menu and choose the "Run" option. The ARM AXD Debugger will be invoked. The Angel Debug Monitor will be started and the randtest application will be run. The console window will display the results of ten calls to the randomnumber() routine.

For more information on using the ADS, refer to the reference manual and user's guide in the Program Files\ARM\ARM Developer Suite\pdf directory or to the ARM web site at <u>http://www.arm.com</u>. A software kit containing Angel sources, images, and build directions for the SA-1110 Development Platform are provided on Intel's website at <u>http://www.developer.intel.com</u> under the StrongARM processors products software library.

## int<sub>e</sub>l *Theory of Operation*

The SA-1110 Development Platform is designed for the hardware and software development of hand-held, palm-top and tethered applications. The SA-1110 Development Platform provides all the system components necessary for a Windows\* CE or other OS hand-held PC system or a sub-notebook system development platform including three independent video heads, high-quality stereo sound and radio interface support.

## 3.1 System Partitioning

The SA-1110 Development Platform's system partitioning is designed so that the SA-1110 Development Board functions as a standalone palm-size PC reference design. The SA-1110 Development Board's mechanical design supports simple system packaging using sheet Lexan\*, screws and spacers to integrate the LCD, optional frontlight, touch screen and batteries.

The block diagram shown in Figure 3-1 illustrates the modularity and flexibility of the design. Two 140-pin fully buffered daughter board expansion headers (J2) are supported; one on each side of the SA-1110 Development Board. Either side of J2 can be used to support the SA-1111 Development Module or the graphics accelerator module.

The functionality of the dual interconnects is identical. The rationale for two interconnects is as follows: When the cards are connected in an extended fashion ("Z" shaped), full electronic probing is possible. When connected in a compact format ("U" shaped), tight packaging is facilitated.

#### Figure 3-1. Intel<sup>®</sup> StrongARM\* SA-1110 Development Platform Block Diagram

As shown in Figure 3-2, the system partitioning allows the SA-1110 Development Board to be used by itself as a minimal palm-size PC system. All device interfacing is implemented with in-system programmable CPLDs and most system interface points are available on connectors suitable for daughter boards or cables.

Although not intended as a ready to manufacture product design, the SA-1110 Development Board provides the basis for low-cost derivative designs. Figure 3-3 shows how data flows within the SA-1110 Development Module.

The SA-1110 Development Board supports the following applications:

- Palm-size PC with docking USB PC sync

- MP3 HiFi stereo record and playback

- Hand writing recognition

- Speech recognition

- Web browser

- VoIP with voice dialing and speakerphone

- Wireless voice dialing VoIP/POTS handset or speakerphone using CF RF modem

- POTS voice dialing speakerphone

- Video capture with CMOS camera and video capture daughter board

- Broadcast TV receiver using video capture daughter board with Microtune® TV tuner chip

- IBM 340 Mb compact flash microdrive applications

## Hardware Considerations

## 4

This chapter provides an in-depth description on the following topics:

- Xbus expansion headers

- Storage

- GPIOs

- Registers

- Displays

- Buses and Ports

- Power

- Audio

- Video

### 4.1 Xbus Expansion Headers

The general-purpose expansion bus headers provided on the SA-1110 Development Board are referred to as the Xbus headers (not to be confused with ISA Xbus). All SA-1110 address, data and memory interface signals are buffered before driving the Xbus headers.

The Xbus headers allow interfacing to the SA-1111 microprocessor companion chip and the SA-1111 Development Module as well as a third-party graphics chip daughter board.

These general-purpose expansion headers allow the use of the SA-1110 Development Board as a general-purpose hardware and software development platform for battery-powered and tethered applications. For more information about Xbus headers, see the *Intel<sup>®</sup> StrongARM<sup>\*</sup> SA-1111 Development Module User's Guide.*

### 4.2 Storage

This section describes the memory map, the SDRAM interface, the expansion flash memory, the interface for the expansion SDRAM, and compact flash issues.

### 4.2.1 Intel<sup>®</sup> StrongARM<sup>\*</sup> SA-1110 Development Board Memory Map

Table 5-1 shows the address ranges for the standard SA-1110 Development Board Xbus devices as well as flash memory, SDRAM, and system control and system debug registers. The address range field indicates the entire decoded range while the size:width field indicates the actual resource size and width within the decoded range. All decoded resources are address wrapped within their address range.

#### Table 4-1. System Memory Map

| Address Range       | Resource<br>Size                                                    | Use                                            | SA-1110 Development Board<br>Size: Width    |

|---------------------|---------------------------------------------------------------------|------------------------------------------------|---------------------------------------------|

| E800,0000-FFFF,FFFF | Reserved 384 Mbyte                                                  | Reserved                                       | —                                           |

| E000,0000-E7FF,FFFF | Zeros Bank 128 Mbyte                                                | Cache flush                                    | Read zeros, no bus cycle                    |

| D800,0000-DFFF,FFFF | SDRAM bank 3 128 Mbyte                                              | Empty                                          | _                                           |

| D000,0000-D7FF,FFFF | SDRAM bank 2 128 Mbyte                                              | Expansion SDRAM bank<br>on SA-1111 board Clk/4 | 16 Mbyte/32 Mbyte/64 Mbyte:<br>32 bits wide |

| C800,0000-CFFF,FFFF | SDRAM bank 1 128 Mbyte                                              | Empty                                          | —                                           |

| C000,0000-C7FF,FFFF | SDRAM bank 0 128 Mbyte                                              | Main SDRAM bank on SA-<br>1110 board Clk/2     | 16 Mbyte/32 Mbyte/64 Mbyte:<br>32 bits wide |

| B000,0000-BFFF,FFFF | LCD and DMA Control<br>256 Mbyte                                    | Internal                                       | _                                           |

| A000,0000-AFFF,FFFF | Memory Control<br>256 Mbyte                                         | Internal                                       | _                                           |

| 9000,0000-9FFF,FFFF | SA-1110 System Control<br>Module Register <sup>a</sup><br>256 Mbyte | Internal                                       | _                                           |

| 8000,0000-8FFF,FFFF | Peripheral Control<br>256 Mbyte                                     | Internal                                       | _                                           |

| 5000,0000-7FFF,FFFF | Reserved 768 Mbyte                                                  | Reserved                                       | —                                           |

| 4800,0000-4FFF,FFFF | CS5 128 Mbyte                                                       | GFX (uses rdy)                                 | TBD bytes: 32 bits wide                     |

| 4000,0000-47FF,FFFF | CS4 128 Mbyte                                                       | SA-1111 (uses Rdy)                             | 8KB                                         |

| 3000,0000-3FFF,FFFF | PCMCIA/CF Slot B 512<br>Mbyte                                       | Compact Flash                                  | 2x2KBytes: 16 bits wide                     |

| 2000,0000-2FFF,FFFF | PCMCIA/CF Slot A 512<br>Mbyte                                       | PCMCIA (SA-1111)                               | 3x64 MBytes: 16 bits wide                   |

| 1800,0000-1FFF,FFFF | CS3 128 Mbyte                                                       | Ethernet device (uses rdy)                     | 1Kbytes: 8 bits wide                        |

| 1000,0000-17FF,FFFF | CS2 128 Mbyte                                                       | SA-1110 Development<br>Board system registers  | Various widths                              |

| 0800,0000-0FFF,FFFF | CS1 128 Mbyte                                                       | Expansion flash on<br>SA-1111 board            | 16/32 MBytes: 32 bits wide                  |

| 0000,0000-07FF,FFFF | CS0 128 Mbyte                                                       | Boot/Application flash<br>ROM on SA-1110 board | 16/32 MBytes: 32 bits wide                  |

a. This register is located in the SA-1110 device.

### 4.2.2 Flash Memory

The SA-1110 Development Board flash bank is populated with 128 Mbit fast page mode 3 V StrataFlash memory. These devices allows 32 Mbyte flash banks.

### 4.2.3 Main SDRAM Interface

The SA-1110 Development Board provides support for 64 Mbit, 128 Mbit or 256 Mbit SDRAMs. The 54 pin TSOP footprint supports a wide variety of SDRAM vendors and densities. The system partitioning is designed to minimize the loading and etch length on the SA-1110 pin bus. This permits the system to run up to 103 MHz SDRAM using SA-1110 CoreClk/2 and 125 MHz SDRAM components. Using two 256 Mb 16 Mx16 SDRAMs provides a main memory load of 64 MBytes. The SA-1110 Development Board is configured with 128 Mb SDRAMs for a 32 MByte memory load.

### 4.2.4 Expansion Flash Memory

The SA-1111 Development Module flash bank is populated with 128 Mbit socketed fast page mode 3V StrataFlash memory devices. These devices allow 32 Mbyte flash banks.

Switch component SW2, switch 8 on the SA-1111 Evaluation Module allows selection of either the main flash bank on the SA-1110 Development Board or the expansion flash bank on the SA-1111 Development Module as the boot bank. For more information on the effects of SW2, see the *Intel*<sup>®</sup> *StrongARM*<sup>\*</sup> SA-1111 Companion Chip Development Board User's Guide.

### 4.2.5 Expansion SDRAM Interface

The SA-1111 Development Module provides support for 64 Mbit, 128 Mbit or 256 Mbit SDRAMs. The 54 pin TSOP footprint supports a wide variety of SDRAM types and sizes. The SA-1111 Development Module's SDRAMs are buffered from the SA-1110 CPU and must run on a SA-1110 CoreClk/4 permitting a maximum SDRAM clock speed of 51.5 MHz for this SDRAM bank. Using two 256 Mb 16Mx16 SDRAMs provides a expansion memory load of 64 Mbytes. The SA-1111 Development Module is initially configured with 128 Mb SDRAMs for a 32 Mbyte memory load.

### 4.2.6 Compact Flash

The SA-1110 Development Board supports a single type II CF socket. The SA-1110 Development Board CF slot uses the same interface signals required by the SA-1111 Development Module and graphics accelerator boards, therefore the CF socket on the SA-1110 Development Board only functions when there are no daughter boards present.

*Caution:* Do not plug a CF card plugged into the SA-1110 Development Board CF socket when the SA-1111 Development or graphics boards are present or it will crash the system and may damage the SA-1111 component, the graphics accelerator device or SA-1110 Development Board's transceiver component. The buffer and transceiver chips on the SA-1110 Development Board that normally drive the CF socket are reconfigured to become the system buffers and transceivers that are used to isolate the SA-1111 Development Module and graphics boards from the SA-1110 Development Board when the daughter boards are attached.

E11, which is shown on sheet 4 of 12 on the *Intel*<sup>®</sup> *StrongARM*<sup>\*</sup> *SA-1110 Development Board Schematics*, is a CPLD that controls the transceivers and some of the CF support signals. In addition, GPIO bits 5:4 control the flash size, as shown in Table 4-5. The SA-1110 GPIO pins GPIO 21, GPIO 22, GPIO 24 and GPIO 25 serve dual functions in the SA-1110 Development Board CF design. When the SA-1111 Development Module is attached, GPIO 22 GPIO 21 are configured to be the GPIO alternate function bus DMA control signals nMBREQ and nMBGNT while GPIO 24 and GPIO 25 are the graphics and SA-1111 interrupt inputs. When the SA-1111

Development Module is not attached and the SA-1110 Development Board CF slot is active then GPIO 21 and GPIO 22 are used as CF RDY interrupt signals and CF card detect interrupt while GPIO 24 ad GPIO 24 are used as CF BVD2 and CF BVD1 inputs.

*Note:* The SA-1110 Development Board CF slot is addressed in the same address space as the SA-1111 Development Module's CF and PCMCIA slots, however the CF slot control signals and interrupt signals are not the same. Refer to the *Intel<sup>®</sup>StrongARM*<sup>\*</sup> SA-1111 Companion Chip Developer's Manual for the details. Two versions of the CF drivers are required for the SA-1110 Development Platform, one for the SA-1111 Development Module and one for the SA-1110 Development Board.

Several key functions available in CF devices are:

- Ethernet interface

- High speed modem

- Wireless one way and two way paging

- IBM micro-drives up to 340 Mbyte

- Bluetooth<sup>1</sup> RF modules

## 4.3 Intel<sup>®</sup> StrongARM<sup>\*</sup> SA-1110 GPIO Usage

The SA-1110 Development Board system maps the SA-1110 GPIO pins as shown in Table 5-4. The table shows the GPIO mapping of SA-1110 Development Board and previous Intel<sup>®</sup> StrongARM<sup>\*</sup> development platforms for comparison and as an aid to OS and Angel porting.

<sup>1.</sup> For the Phase 5 release of this product, formal Bluetooth interface specifications were not available. For more information, see section Section 4.13.3.

*Note:* GPIO 0 and GPIO 1 are the only wake up events that can cause the SA-1110 to come out of sleep mode if sleep mode was entered as a result of VDD\_FAULT or BATT\_FAULT signals.

#### Table 4-2. GPIO Usage for Intel<sup>®</sup> StrongARM<sup>\*</sup> Platforms

| GPIO | SA-1100 Development<br>Platform <sup>a</sup> | SA-1100 Multimedia and SA-1101<br>Development Boards <sup>b</sup> | SA-1110 Development Platform |

|------|----------------------------------------------|-------------------------------------------------------------------|------------------------------|

| 27   | 32 KHz Out                                   | 3.68 MHz Out                                                      | 3.68M_32K                    |

| 26   | RCLK_Out                                     | GPIO or RCLK_Out                                                  | VBATT_LOW_IRQ/RCLK           |

| 25   | KBC_ATN#                                     | Keypad IRQ/Xbus_spare                                             | SA111_IRQ_CF_BVD1            |

| 24   | KBC_WUKO                                     | SideKick IRQ                                                      | GFX_IRQ_CF_BVD2              |

| 23   | KBC_WKUP#                                    | UCB_IRQ                                                           | UCB1300_IRQ                  |

| 22   | IRQ_C#                                       | nMBREQ                                                            | nMBREQ_CF_CardDetect         |

| 21   | IRDA_SD                                      | nMBGNT                                                            | nMBGNT_CF_IRQ                |

| 20   | LED_RED#                                     | I2C SDA                                                           | UART3_CLK/SPARE              |

| 19   | SDLC_GPI                                     | I2C SCL                                                           | STEREO_64FS_CLK              |

| 18   | SDLC_HSKI                                    | FIFO_IRQ                                                          | L3_I2C_SCL                   |

| 17   | SDLC_AAF                                     | Xbus_spare                                                        | L3_MODE (LED)                |

| 16   | SDLC_HSKO                                    | Xbus_spare                                                        | PS_MODE_SYNC                 |

| 15   | UART_RXD                                     | UART_RXD                                                          | L3_I2C_SDA                   |

| 14   | UART_TXD                                     | UART_TXD                                                          | RADIO_IRQ                    |

| 13   | SSP_SFRM                                     | Header SSP_SFRM/spare                                             | SSP_UDA1341_SFRM             |

| 12   | SSP_SCLK                                     | Header SSP_SCLK/spare                                             | SSP_UDA1341_SCLK             |

| 11   | SSP_RXD                                      | Header SSP_RXD/spare                                              | SSP_UDA1341_RxD              |

| 10   | SSP_TXD                                      | Header SSP_TXD/spare                                              | SSP_UDA1341_TxD              |

| 9    | LCD_D15/LED_GRN1#                            | LCD_D15                                                           | LCD_D15_CNFG7                |

| 8    | LCD_D14/LED_GRN2#                            | LCD_D14                                                           | LCD_D14_CNFG6                |

| 7    | LCD_D13/P1_F1#                               | LCD_D13                                                           | LCD_D13_CNFG5                |

| 6    | LCD_D12/P1_IREQ#                             | LCD_D12                                                           | LCD_D12_CNFG4                |

| 5    | LCD_D11/P1_STSCHG#                           | LCD_D11                                                           | LCD_D11_CNFG3                |

| 4    | LCD_D10/P0_F1#                               | LCD_D10                                                           | LCD_D10_CNFG2                |

| 3    | LCD_D9/P0_IREQ#                              | LCD_D9                                                            | LCD_D9_CNFG1                 |

| 2    | LCD_D8/P0_STSCHG#                            | LCD_D8                                                            | LCD_D8_CNFG0                 |

| 1    | SW1                                          | SW1/SW 7:0_IRQ/alt FIFO IRQ                                       | ON_OFF_SW2_or_FIQ            |

| 0    | SW0                                          | SW0/DSP_IRQ/SW 7:0_IRQ                                            | ON_OFF_SW1                   |

Order number DE-1S110-OA Order number DE-1S110-OC a. b.

| GPIO | SA-1100 Development<br>Platform <sup>a</sup> | SA-1100 Multimedia and SA-1101<br>Development Boards <sup>b</sup> | SA-1110 Development Platform |

|------|----------------------------------------------|-------------------------------------------------------------------|------------------------------|

| 9    | ADC_SYNC                                     | ACD_SYNC                                                          | ADC_SYNC                     |

| 8    | DAA_OH                                       | DAA_OH                                                            | DAA_OH (LED)                 |

| 7    | DAA_RI#                                      | DAA_RI#                                                           | DAA_RI-                      |

| 6    | RED_LED#                                     | 7 segment dot LED                                                 | CLID (caller ID)             |

| 5    | GRN_LED#                                     | NOT USED                                                          | FuncSW6                      |

| 4    | SEVEN_SEG_BLANK                              | NOT USED                                                          | FuncSW5                      |

| 3    | SEVEN_SEG_LED[3]                             | NOT USED                                                          | FuncSW4                      |

| 2    | SEVEN_SEG_LED[2]                             | NOT USED                                                          | FuncSW3                      |

| 1    | SEVEN_SEG_LED[1]                             | NOT USED                                                          | FuncSW2                      |

| 0    | SEVEN_SEG_LED[0]                             | NOT USED                                                          | FuncSW1                      |

#### Table 4-3. UCB 1300 CODEC

a. Order number DE-1S110-OA

b. Order number DE-1S110-OC

### 4.3.1 GPIO 0 and GPIO 1

When the SA-1111 Development Module and Angel debug monitor are attached, GPIO 0 and GPIO 1 have special use at system boot time. The Angel boot software reads the SA-1110 GPIO 0 and GPIO 1 to determine which of four boot images to jump to. After system reset, GPIO 0 and GPIO 1 are driven through the SA-1111 Development Module's test CPLD from switch pack SW2, switches 1 and 2. After boot time, the GP01\_OFF bit in the NCR may be set to three-state the CPLD GPIO 0 and GPIO 1 drivers and allow these GPIOs to be used as their normal functions.

When the SA-1110 Development Board is used without the SA-1111 Development Module, the GPIO 0 and GPIO 1 signals are used for the soft power on/off switches and a spare fast interrupt (FIQ) signal.

If the Angel boot software is run on the SA-1110 Development Board without the SA-1111 Development Module attached, then S1 and S2 on the SA-1110 Development Board, which drive GPIO 0 and GPIO 1, can be used to select the Angel boot vector.

## 4.3.2 Intel<sup>®</sup> StrongARM<sup>\*</sup> SA-1110 GPIO Pin Descriptions

Details of the SA-1110 GPIO pins are shown in Table 5-4. *Pin Name* indicates the actual name of the pin on the SA-1110 device, while *Signal Name* indicates the signal name and function on the SA-1110 Development Module.

#### Table 4-4. GPIO Pin Descriptions (Sheet 1 of 2)

| Pin Name  | Signal Name                    | Description                                                                                                                                                                                                   |  |

|-----------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|           |                                | Main system software control on/off switch                                                                                                                                                                    |  |

| GP[0]     | On_Off_Sw1                     | Application dependent switch. Used to toggle main system power between run and sleep modes.                                                                                                                   |  |

|           | 0.0".0.0                       | Secondary system software control on/off switch                                                                                                                                                               |  |

| GP[1]     | On_Off_Sw2<br>and Spare<br>FIQ | Application dependent switch. Used to toggle backlight power on and off. May function a<br>one touch record button that wakes up system to record audio.                                                      |  |

|           | i i i i i                      | Secondary function as a spare FIQ interrupt if required by GFX board.                                                                                                                                         |  |

|           |                                | LCD data for upper 8 bits of 16 bit color                                                                                                                                                                     |  |

|           | LCD_D(15:8)                    | After system boot, these pins should be configured to drive the upper LCD data bits.                                                                                                                          |  |

| GP[9:2]   | CNFG(7:0)                      | System configuration information                                                                                                                                                                              |  |

|           | CINI C(7.0)                    | At system boot time, GPIO 9:2 may be read to determine system configuration. Refer to CNFG table.                                                                                                             |  |

| GP[13:10] | SSP_<br>UDA1341                | SSP UDA1341 stereo codec port                                                                                                                                                                                 |  |

|           |                                | Radio Interrupt request                                                                                                                                                                                       |  |

| GP[14]    | Radio_IRQ                      | 0 – No interrupt                                                                                                                                                                                              |  |

| 01[14]    | Itaulo_Itte                    | 1 – Interrupt                                                                                                                                                                                                 |  |

|           |                                | Only available when radio board is attached.                                                                                                                                                                  |  |

|           | L3_SMB_<br>SDA                 | Shared L3 and SMB control ports                                                                                                                                                                               |  |

| GP[15]    |                                | SMB data                                                                                                                                                                                                      |  |

| 0[[10]    |                                | L3 data is part of the L3 control bus to the UDA1341 stereo codec.                                                                                                                                            |  |

|           |                                | The System Management Bus (SMBus) is used to control smart battery chips                                                                                                                                      |  |

|           |                                | Power supply mode and sync control                                                                                                                                                                            |  |

|           | PSMODE                         | 0 – Low power operation for sleep mode                                                                                                                                                                        |  |

| GP[16]    | SYNC                           | 1 – High power, low noise operation for run mode                                                                                                                                                              |  |

|           |                                | Sync – Program SDLC clock out to synchronize power switches. Used to reduce RFI an video or audio noise                                                                                                       |  |

|           |                                | L3 mode signal with LED                                                                                                                                                                                       |  |

| GP[17]    | L3_MODE<br>LED                 | L3 MODE is part of the L3 control bus to the UDA1341 stereo codec.                                                                                                                                            |  |

| 0.[]      |                                | This GPIO has a LED that may be used by the boot code to indicate boot status by flashing codes. After boot time this GPIO must function as the UDA1341 MODE signal.                                          |  |

|           |                                | Shared L3 and I2C control ports                                                                                                                                                                               |  |

| GP[18]    | L3_I2C_SCL                     | I2C clock                                                                                                                                                                                                     |  |

|           | 20_120_002                     | L3 clock is part of the L3 control bus to the UDA1341 stereo codec.                                                                                                                                           |  |

|           |                                | SCL is used as System Management Bus (SMBus) to control smart battery components                                                                                                                              |  |

| GP[19]    | SSP_UDA<br>1341<br>Extrn_Clk   | SSP UDA1341 stereo codec external clock input                                                                                                                                                                 |  |

|           | 1                              | UART3 Clock input                                                                                                                                                                                             |  |

| GP[20]    | UART3 CLK/<br>SPARE            | User to provide high speed clock to UART3. UART3 is used as the radio communication port. Bluetooth radio may require use of the external UART3 clock. Also a possible spar GPIO if Bluetooth is not present. |  |

| 001041    | MBGNT                          | MBGNT SA-1110 DMA bus grant signal when SA-1111 development is attached                                                                                                                                       |  |

| GP[21]    | CF_IRQ                         | CF_IRQ compact flash interrupt when no daughter boards are attached                                                                                                                                           |  |

| Pin Name  | Signal Name       | Description                                                                                   |  |

|-----------|-------------------|-----------------------------------------------------------------------------------------------|--|

|           |                   | MBREQ SA-1110 DMA bus request signal when the SA-1111 Development Module is attached          |  |

| ODIOOI    | MBREQ             | CF compact flash card detect interrupt when no daughter boards are attached                   |  |

| GP[22]    | CF_<br>CardDetect | CF_CD1 and CF_CD2 are logically AND'ed on the SA-1110 Development Board                       |  |

|           | Calubelect        | 0 – CF card present                                                                           |  |

|           |                   | 1 – CF card absent                                                                            |  |

| GP[23]    | UCB1300_<br>IRQ   | UCB1300 Codec, UCB_GPIO and touch screen interrupts                                           |  |

| GP[24]    | GXF_IRQ           | Graphics daughter board interrupt                                                             |  |

| GF[24]    | CF_BVD2           | CF_BVD2 signal when no daughter boards are attached                                           |  |

| GP[25]    | SA-1111_IRQ       | SA-1111 Development Module interrupt                                                          |  |

| 01 [23]   | CF_BVD1           | CF_BVD1 signal when no daughter boards are attached                                           |  |

|           | VBATT_LOW         | VBATT_LOW_IRQ Low battery interrupt                                                           |  |

| GP[26]    | _IRQ<br>RClk      | RClk, CPU coreclk/2 to clock logic analyzer pods when SA-1111 Development Module is attached. |  |

| GP[27]    | 3.68M_32K         | 3.68 MHz SA-1111 and GFX PLL reference clock and GFX 32 KHz power up clock                    |  |

| GP[31:28] | Reserved          | -                                                                                             |  |

#### Table 4-4. GPIO Pin Descriptions (Sheet 2 of 2)

### 4.4 Register Descriptions

This section describes the following registers:

- System configuration register—to control SDRAM size, flash size, and type of module such as SA-1111 development module.

- Board configuration register—to control the compact flash, codec, IRDA, stereo, audio, LCD, RS232, LEDs, communication ports, charger, radio, and speaker.

- Board status register—to control communications and radio ports.

## 4.4.1 Intel<sup>®</sup> StrongARM<sup>\*</sup> SA-1110 System Configuration Register SCR

The SA-1110 Development Board supports several different SDRAM and flash memory types and sizes as well as different LCD types and multiple daughter cards. To allow the system boot code to correctly configure the SA-1110 memory interface and timing registers, the SA-1110 Development Board uses GPIO 9:2 pins to input system configuration information at boot time.